從聊天機器人程式ChatGPT,到文生視頻大模型Sora,AI大模型的蓬勃發展背後,為演算法模型、高品質數據、算力基礎設施帶來了持續的挑戰。“當企業通過Scale out提升集群規模,就需要把數據中心從微觀到宏觀、點對點地連接起來,增強各個層面的互聯性能,真正有效地應用算力資源。” 奇異摩爾創始人兼CEO田陌晨在接受電子發燒友採訪時表示。

伴隨著摩爾定律的放緩步伐,通過Scale up提升單處理器系統的性能和算力遭遇了“流水線過長,延遲高、佈線困難”等重重困境。Scale out作為Scale up的延續,在物理層面引入了規模性互聯,讓“算力-互聯”成為算力提升的新型抓手。研究機構IPnest預測,2025年,“片間互聯技術”介面IP市佔率有望超過處理器IP,成為排名榜首的IP品類。那麼,片內、片間、網間的互聯技術未來會呈現何種特點?高性能計算體系將如何發展?就這些話題,我們採訪了互聯技術領域代表企業奇異摩爾CEO田陌晨先生。

片內互聯:從專用到通用

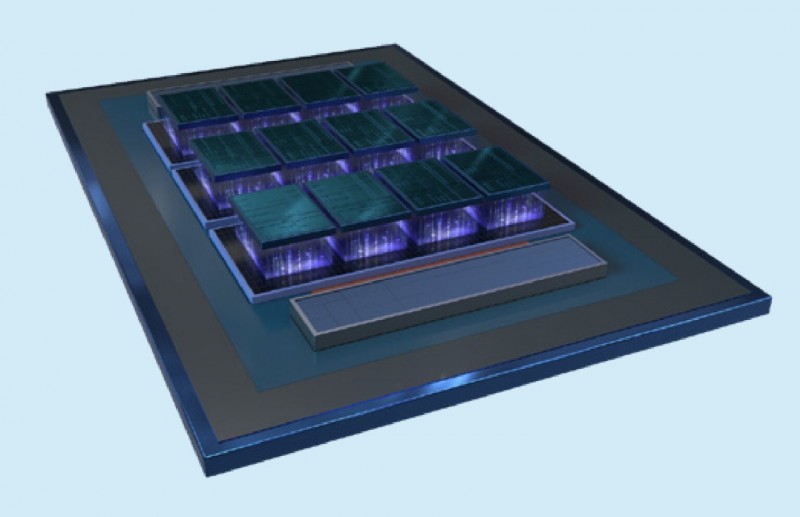

理論上,芯粒可被視作固定模組,實現不同産品、代際的復用。在智算中心集群發展中,以互聯芯粒IO Die為代表的互聯芯粒在提升良率、降低製造複雜度和成本等方面所顯示出的優勢,已成為行業發展共識。AMD的Zen系列和英特爾Clearwater Forest旗艦級數據中心處理器都是典型案例。

Intel Clearwater Forest 2

田陌晨認為,IO Die為代表的片內互聯技術呈現芯粒化、3D化發展兩大趨勢。芯粒化是為了增進架構靈活性,降低晶片對先進工藝的依賴;3D化則是通過縱向維度進一步提升互聯密度。

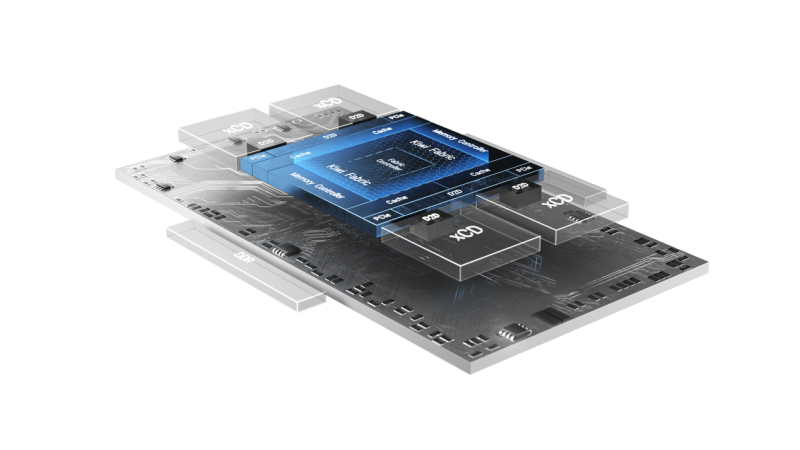

目前,市場上的IO Die主要為AMD、英特爾等大廠主導,但私有協議無法相容不同來源的芯粒,專用IO Die的封閉生態已成為其發展掣肘。受到巨大的需求推動,通用IO芯粒開始嶄露頭角。以奇異摩爾旗下的通用互聯芯粒 Kiwi IO Die為例,産品整合了如D2D\DDR\PCIe\CXL等大量存儲、互聯介面,最高可以支援10+Chiplets,構建高達192 core CPU或1000T GPU的算力平臺。

奇異摩爾通用互聯芯粒 Kiwi IO Die

與其同時,受益於先進封裝技術的進步,IO Die也出現了2.5D向3D的結構變化。Base Die可視為IO Die的3D形態,允許不同計算、存儲芯粒的堆疊或並排放,可顯著提升晶片單位面積電晶體的整合度,帶來更高的頻寬,更低的延遲、功耗。

市場上Base Die的境況與IO Die類似,雖然專用産品已在市場上展現了商業化價值,但技術並未擴散,而是被少數頭部企業壟斷。在奇異摩爾為代表的創新企業努力下,Base Die通用市場開始起步。據田陌晨介紹,奇異摩爾旗下的通用互聯底座Kiwi 3D Base Die,在3D高性能通用底座方面屬全球首例,實現了通用互聯芯粒在頻寬、能效、搭載晶片數量等多方面的突破性進展,能夠以20%的功耗實現8倍于2.5D結構的互聯密度,最高可實現16顆算力芯粒堆疊。

IO Die和Base Die只是互聯技術的兩個典型的例子,説明片內互聯技術如何在計算與存儲之間、在龐大的智算中心和Scaling out 的浪潮中,産生對計算能力的更多助力。事實上,除了片內互聯,還有許多種方法可以讓更多的數據實現更高好的連接和更低的成本,比如片間互聯、網間互聯技術的單點到全面突破。

亟待加速的片間互聯:D2D介面

和片內互聯一樣,受益於算力和突飛猛進的算力增長需求,片間互聯技術亟需加速。基於Chiplet技術的Die-to-Die技術(D2D)帶來了一種更高效的計算和記憶體的連接方式,可以看似毫不費力的將計算、存儲芯粒整合在一起,在互聯層面上形成一個SoC級晶片。

相比傳統的計算晶片和存儲晶片的互聯方式,D2D提供了更高效、更低延遲的連接方式,是Chiplet實現的基礎,田陌晨介紹。通過Die間通信,D2D可以實現更高的傳輸頻寬和更高密度的整合;D2D能有效縮短數據傳輸的物理距離,降低延遲,提高處理速度;作為先進封裝的基礎,D2D可以實現計算和存儲單元的無縫連接,進一步提高性能、降低功耗;基於D2D,企業可以更靈活地實現計算和存儲單元的多模組配置,提高系統可擴展性、靈活性,降低系統維護成本。這些優勢,使得D2D介面在高性能集群的Scaling out建設中,發揮了關鍵的作用。

和IO Die一樣,D2D也需要通用化的大力推進。奇異摩爾基於UCIe標準,推出了全球首批支援 UCIe V1.1 的 Die2Die IP,互聯速度高達32GT/s,延時低至數nS,全面支援UCIe、CXL、Streaming等主流協議,即插即用。田陌晨説,奇異摩爾所有産品都構建在國際標準協議之上,致力於使各家産品實現互聯互通,構成一個開放的Chiplet系統。

RISC-V+Chiplet:1+1>2

如今,Chiplet之外,RISC-V架構也在大舉邁進高性能計算。邊緣計算市場,傳統通用型MCU/MPU/CPU已經難以滿足不同應用場景和性能要求,RISC-V了帶來更好的PPA實現。RISC-V的本質是一個開放標準,衝擊高性能運算市場是發展的必然,而二者(與Chiplet)的融合,被認為能為高性能計算市場開闢一場1+1>2的創新動力。這也是RISC-V高性能處理器的代表性企業Ventana與奇異摩爾合作的深層動因。

Ventana創始人兼CEO Balaji Baktha介紹,兩家企業聯手打造了一個可擴展處理器架構,可將多個Ventana Veyron V2與奇異摩爾的IO Die組成不同配置的SoC。田陌晨認為,V2與奇異摩爾IO Die的結合,是RISC-V和Chiplet在高性能計算領域融合的成功案例。

“RISC-V具備開源、開放、靈活和高度可定制特性,設計了多種用於任務加速的指令集擴展,能實現向量計算、加解密等任務加速,具有較高的計算性能,且簡潔特性能降低晶片的功耗。”Balaji説,“而Chiplet是構建下一代半導體産品前進戰略的重要組成部分,可以輕鬆構建高性能CPU。其‘可組合性’讓用戶以最佳比例組合計算、記憶體和IO,創造一個在性能、成本效益、工作負載等各方面都更為高效的系統。將RISC-V的開放式架構與 Chiplet開放式硬體設計相結合,能有效推動數據中心的工作流程效率,將單插槽性能發揮到極點。”

記者了解到,奇異摩爾和Ventana一直在努力將RISC-V和IO Die的組合推向下一代計算架構的前沿,以提高數據中心服務的效率和工作負載的效率,並共同創建了一款高性能數據中心級RISC-V處理器,其融合了RISC-V 架構和模組化的Chiplet設計的優勢,每個V2單元包括32個核心,最終實現最高192個內核,這也是全球首例數據中心級的RISC-V Chiplet處理器。

回顧這次和Ventana的合作,田陌晨稱,從技術互通性角度看,基於IO Die的互聯,x86、ARM和RISC-V三大架構都需要採用大量存儲訪問和外部介面,進行大量傳輸、讀取及調度。RISC-V和Chiplet技術融合進一步提升了計算平臺的定制特性,可以避免那些對高性能運算有需求的客戶被鎖定在一個供應商的生態內,並助力企業應對AGI所引發的架構變革挑戰,這在x86和ARM的Chiplet設計中較難實現。

當然,RISC-V和Chiplet技術融合,也伴隨著如Die間通信、高性能、特定領域等多重挑戰,如,為實現不同來源芯粒的通信,兩家公司採取了IO Die中央設計連接CPU芯粒的方案,通過Kiwi Fabric實現了ns級的低延遲和高效的數據傳輸。讓整個SoC在工作流的角度上,呈現獨立CPU的特質。

在性能方面,為達到現有ISA(x86/ARM)設定的高性能基準,確保處理器微架構可以提供世界一流性能,雙方合作的産品最高可實現192個內核。同時,通過一致性互聯,讓所有內核共用高性能、高速暫存和記憶體。

在特定領域方面,通過對計算芯粒、記憶體和各種加速器配比的整體規劃,為各種工作負載提供靈活的硬體配置選項;在CPU中內置了端到端的RAS,確保所有總線都受到安全啟動驗證和級別驗證等保護,同時克服側通道攻擊和其他漏洞,確保CPU芯粒和整個SoC層面的安全。

從計算加速到網路加速

從行業動態來看,高性能運算從Scale up向Scale out的轉變是全方位的,在晶片設計、算力卡間、集群間無不如此。簡單的説,Scale out最核心的改變就是互聯。田陌晨認為,在Scale out所引發的巨量數據交互挑戰背後,是加速重點從計算到網路的轉變和“Bandwidth, Efficiency, Workload”互聯三要素的優化需求。

在算力集群網路傳輸協議方面,傳統協議TCP/IP存在CPU負載重、延遲高等缺點,難以滿足高性能計算對網路吞吐、時延的苛刻要求。RDMA能直接通過網路介面訪問記憶體數據,無需作業系統內核的介入,讓大規模並行計算集群成為可行。電腦網路協議棧將從TCP/IP過渡到RDMA,在網路層面上,把一個集群變成一台設備。

RDMA並未規定完整的協議棧,因此包含不同的分支,如英偉達的Quantum InfiniBand是專門為RDMA設計的一種超低延遲、超高吞吐量的專用網路引擎。然而,業界需要一種更為通用化的解決方案。在性能方面可與InfiniBand匹敵的RoCE顯著降低了RDMA協議通信成本,被認為能夠打破英偉達在這個領域的技術壟斷。

這也是奇異摩爾推出高性能網路加速芯粒Kiwi NDSA(Network Domain Specific Accelerator)系列的原因所在。據介紹,Kiwi NDSA內建RoCE V2高性能 RDMA (Remote Direct Memory Access) 和數十種卸載/加速引擎,可作為獨立芯粒,實現系統不同位置的加速。Kiwi NDSA産品系列包括“NDSA-RN-F”和“NDSA-RN”。前者是全球首批200/400G的高性能FPGA RDMA網卡,將在近期面世;後者是全球首款支援800G頻寬的RDMA NIC Chiplet産品,除頻寬升級到800G之外,延時也降至ns級,並支援數十GB的超大規模數據包。

結語

在高性能計算體系全方位從Scale up向Scale out轉變的背景下,互聯技術已成為提升集群算力的新方案。以IO Die為代表的互聯芯粒正在加速其通用化進程和2.5D至3D轉變;片間PCIe等傳統傳輸方式正在被低延遲、低功耗的D2D技術取代;集群網際網路絡則從TCP/IP轉向RDMA架構,通用RDMA方案將迎來更廣闊的機遇。互聯技術和RISC-V架構的融合,能夠助力企業更好地應對AGI所引發的架構變革挑戰,幫助高性能計算領域用戶實現Scale out。未來,對幾乎每一家高性能計算産業鏈上的企業來説,互聯都是一個至關重要的市場。

(推廣)

來源:信陽日報 | 撰稿:奇異摩爾 | 責編:谷晟 審核:張淵

![]() 新聞投稿:184042016@qq.com 新聞熱線:135 8189 2583

新聞投稿:184042016@qq.com 新聞熱線:135 8189 2583